## Calcolatori

#### Reti Combinatorie

#### **COMPARATORE NUMERI NATURALI:**

Compara due numeri naturali A e B e restituisce tre bit (g,e,l) che sono asseriti rispettivamente se A>B, A=B o se A<B. Sono mutuamente esclusivi.

INPUT: A e B naturali

OUTPUT: g, e, l

# A — Generatore Position of Pos

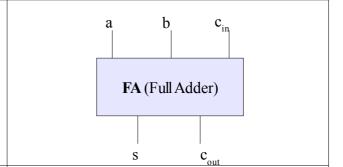

#### **FULL ADDER (SOMMATORE AD UN BIT):**

Somma due bit (a e b) tenendo conto del riporto precedente o *carry* (c<sub>in</sub>) e produce in uscita il bit di somma (s) ed il bit di riporto o *carry* (c<sub>out</sub>)

**INPUT:** a, b, c<sub>in</sub> **OUTPUT:** s, c<sub>out</sub>

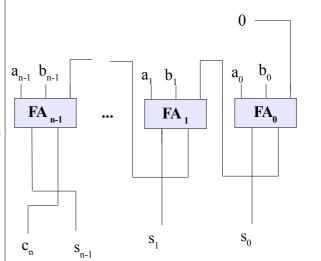

#### **SOMMATORE AD n BIT:**

Il sommatore per numeri naturali di grandezza arbitraria *n* viene realizzato mettendo in cascata *n* Full Adder e collegando il riporto prodotto dall' *i-esimo* Full Adder al carry d'ingresso dell' (*i+1*)-*esimo* Full Adder (**Ripple-Carry**) Naturalmente il primo FA dovra' avere carry d'ingresso = 0

**INPUT:** a,b di lunghezza arbitraria n **OUTPUT:** s risultato di lunghezza n, c<sub>n</sub> bit di riporto della somma

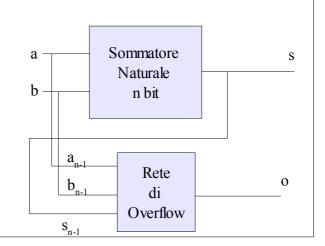

#### **SOMMATORE IN C2:**

Sommare due numeri a e b espressi in complemento a 2 corrisponde ad effettuare (per una prorpietà del C2) una somma di due numeri naturali, non tenedo conto del riporto (carry) e tenendo di conto di una possibile situazione di overfow (che si verifica se a e b hanno segno concorde ed il risultato s ha segno discorde da questi) **INPUT:** a,b di lunghezza n in C2

**OUTPUT:** s risultato di lunghezza n, o bit di overflow

#### **COMPARATORE MSS:**

Compara due numeri binari (a e b) di lunghezza n espressi in modulo e segno. Viene implementato comparando prima i moduli (a<sub>n-2</sub>, ..., a<sub>0</sub> e b<sub>n-2</sub>, ..., b<sub>0</sub>) e tramite una rete combinatoria che gestisce i risultati tenendo di conto del segno di a e del segno di b (ad esempio se a>b in modulo ma sgn(a)=-1 e sgn(b)=1 allora b>a)

PROBLEMA: lo zero viene rappresentato in due modi diversi nella codifica M&S (+0 = 000..0 e -0 = 100..0) per gestire tale problema (e non rischiare che la rete combinatoria reputi diversi per via del segno due numeri che in realta' sono uguali) viene aggiunto un altro modulo combinatorio (**Z**) che ha l'unico compito di controllare il modulo di a ed il modulo di b ed asserire il suo bit d'uscita se |a|=|b|=0.

**INPUT:** a,b di lunghezza n in M&S **OUTPUT:** G, E, L asseriti se a>b, a=b, a<b

###

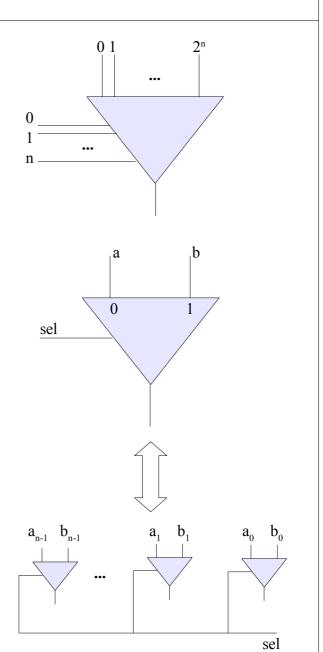

#### **DECODER SU n BIT:**

Il decoder è un dispositivo ad n ingressi e 2<sup>n</sup> uscite. In base alla configurazione in ingresso (ad esempio 101 in un caso di decoder a 3 bit) tale rete combinatoria asserisce l'uscita corrispondente (nell'esempio la 5°) tra quelle possibili. Superfluo dire che le uscite sono mutuamente esclusive.

INPUT: n bit

**OUTPUT:** 2<sup>n</sup> bit (tutte le possibili configurazioni degli ingressi)

# 0 \_\_\_\_\_ 0 1 \_\_\_\_ Decoder n bit ... 2<sup>n</sup>

#### **ENCODER SU n BIT:**

Come il decoder ma il funzionamento è esattamente opposto. Deve essere asserita solo una linea d'ingresso. In

< con ingressi ed uscite invertiti >

caso questo requisito venga a mancare si ha un uscita non specificata

**INPUT:** 2<sup>n</sup> bit **OUTPUT:** n bit

#### **MULTIPLEXER:**

Il multiplexer e' un selettore di ingressi. Esso ha, nel caso generale, 2<sup>n</sup> ingressi "di selezione" ed n ingressi "selettivi". Questi n ingressi codificano uno ed un solo ingresso che verra' scelto e trasferito sul bit d'uscita del componente. Facendo un esempio informatico, esso è simile ad uno *switch*. Analogamente il **demultiplexer** (poco usato in questo corso) effettua l'operazione inversa: a partire da un ingresso, in base a n bit "selettivi" viene scelta una delle 2<sup>n</sup> uscite sulle quali trasferire l'ingresso.

In alcuni casi pero', si ha il problema di dover scegliere tra piu' parole anziche' bit, ad esempio scegliere se mandare in uscita a o b parole di n bit (anche l'uscita dovra' essere di n bit chiaramente). Dovremmo usare in questo caso n multiplexer. Ma notiamo che tali selettori sono azionati dal medesimo bit selettivo, e pertanto è facilmente creabile un multiplexer con ingressi a n bit

**INPUT:** 2<sup>n</sup> bit tra cui scegliere, n bit selettivi

**OUTPUT:** 1 bit scelto

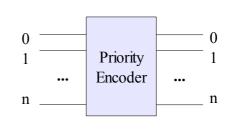

#### PRIORITY ENCODER:

Ad ogni ingresso è associato un valore di priorita' (generalmente decrescente dall'ingresso 0 ... n-1) ed in uscita viene asserita solo la linea corrispondente alla priorita' maggiore.

INPUT: n bit

**OUTPUT:** n bit (mutuamente esclusivi)

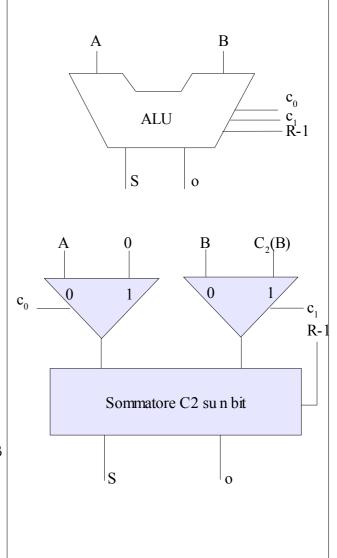

#### ALU:

La ALU (Arithmetic Logic Unit) unisce molti dei concetti precedentemente visti per creare una rete combinatoria capace, in base a dei flag d'ingresso, di eseguire molteplici operazioni tra cui:

- selezione di B

- incremento di B (B+1)

- complementazione di B (B)

- cambio segno di B (-B)

- somma di A e B (A+B)

- sottrazione di A e B (A-B)

Per realizzare tutto questo abbiamo bisogno di un sommatore C2 su n bit e di due multiplexer: uno tra A e 0 che decide se le operazioni saranno su due operandi o se su uno soltanto, ed uno che sceglie tra B ed il complemento di B. Quindi per ora abbiamo due fala (c<sub>0</sub>, c<sub>1</sub>) selettori dei multiplexor. Ma per incrementrare B, cambiare di segno a B  $(\overline{B}+1)$  o sottrarre B ad A  $(A+\overline{B}+1)$  ho bisogno di aggiungere un bit alla somma. Faccio questo mediante il bit di carry del sommatore. Senza molte difficoltà realizzo un encoder nel quale asserendo bit di ingresso come ADD, SUB, INCR B, ...

**INPUT:** A,B parole di n bit, elenco di flag (ADD, SUB, ...) mutuamente esclusivi

codifica c<sub>0</sub>, c<sub>1</sub> ed il carry per eseguire

le operazioni richieste.

**OUTPUT:** s parola di n bit rappresentante il risultato dell'operazione richiesta, bit di overflow

#### Reti Sequenziali

#### FLIP-FLOP SR:

Il flip flop SR e' ottenuto aggiungendo al LETCH due porte and che attivano la transazione solo se il CLK è positivo. Quindi se S=0 e R=0, manitene lo stato corrente, se S=1 (set) pone lo stato futuro ad 1, se R=1 (reset) pone lo stato futuro a 0: La situazione S=1 ed R=1 non deve mai verificarsi.

FUNZIONE: Q'=S+RQ

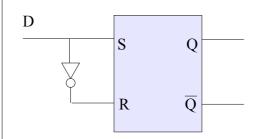

#### FLIP-FLOP D:

Aggiungendo una negazione al flipflop SR otteniamo il flip-flop D. Tale macchina a stati porta esattamente ciò che ha in ingresso come suo stato futuro. Se l'ingresso e' 0 si ha Q'=0+0Q=0 se l'ingresso e' 1 invece Q'=1+1Q=1.

FUNZIONE: Q'=Q

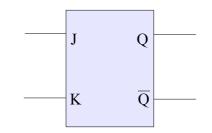

#### FLIP-FLOP JK:

Il flip-flop JK funziona come l'SR salvo il fatto che il caso S=1 R=1 non è più inammissibile, ma in questo caso attiva la funzione toggle che inverta lo stato corrente (Q'= $\overline{Q}$ )

FUNZIONE:  $Q'=J \overline{Q} + \overline{K}Q$

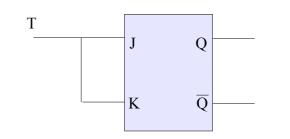

#### FLIP-FLOP T:

Collegando le uscite del JK ad un unico ingresso comune, otteniamo il T. Si vede facilmente che se l'ingresso è 0 si ha una fase di Hold, viceversa lo stato cambia.

FUNZIONE:  $Q'=\overline{1Q} + \overline{\overline{1}Q}$

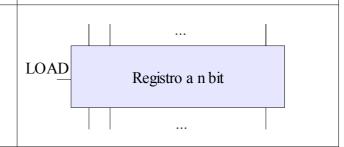

#### **REGISTRO:**

Come visto sopra un flip-flop e' un componente dotato di memoria di un bit. Ora, ponendo vari di questi componenti in cascata possiamo ottenere un componente capace di

memorizzare n bit. Sarà inoltre possibile (tramite una rete combinatoria che funge da interfaccia e tramite un segnale di LOAD) modificare il contenuto di tale memoria. Lo stato è proiettato direttamente sull'uscita e pertanto sempre "accessibile" (non c'è bisogno di un segnale per ablilitare l'output del dato in memoria)

INPUT: il dato da inserire nel registro, LOAD per abilitare l'immissione di quel dato

**OUTPUT:** lo stato rappresentante il valore contenurto nel registro

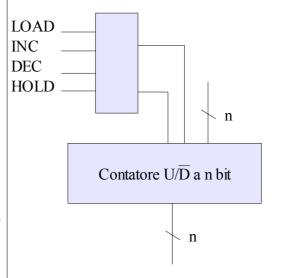

#### **CONTATORI UP/DOWN:**

Non e' difficile realizzare, a partire da dei JK o dei flip-flop T, un oggetto il cui stato commuta ad ogni colpo di CLK. Inoltre, con poca logica sequenziale intorno e ponendo in cascata oggetti del genere (facendo si che l'i+1-esimo commuti sul fronte di salita/discesa dell'i-esimo) e' possibile realizzare oggetti il cui stato complessivo e' su n bit che rappresenta un numero naturale codificato in binario che viene incrementato/decrementato di 1 ogni colpo di CLK. Tale oggetto viene detto contatore.

Tale dispositivo è capace di contare solo da 0 a 2<sup>n</sup>-1. Mediante l'utilizzo di una **rete di controllo** (vedi sotto) appropriata e' possibile generalizzare il concetto di contatore. Per fare questo sono necessari 4 segnali di controllo (codificati poi da un encoder):

- il INC che abilita il contatore a contare UP

- il LOAD che permette di caricare una dato all'interno del contatore attraverso degli appositi ingressi e salvarlo nello

stato (vedi registro)

- DEC che abilita il contatore a contare DOWN

- HOLD manitene lo stato corrente

**INPUT:** LOAD, INC, DEC, HOLD, il possibile dato da immettere nel contatore tramite LOAD

**OUTPUT:** lo stato totale rappresentante il numero "contato"

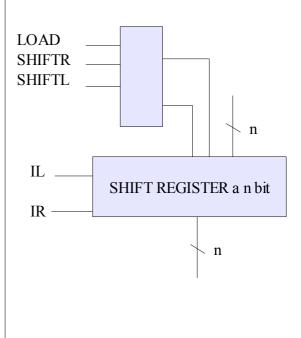

#### SHIFT REGISTER:

Lo *shift register* e' un registro a scorrimento molto utile in particolari circostanze. Tramite dei segnali di controllo permette di:

- HOLD mantenere il contenuto del registro invariato (piu' una possibile codifica degli ingressi che un vero e proprio segnale)

- LOAD caricare un dato nel registro

- SHIFTR spostare l'intero contenuto del registro di un bit verso destra ed inserire un dato in ingresso (IL) nel posto vuoto a sinistra (nota: il bit meno significativo viene perso)

- SHIFTL analogo allo SHIFTR ma verso sinistra. Il dato viene reperito in IR ed il bit piu' significativo ad essere perso.